Baumgan F-65 8/64

PROGRAMMED DATA PROCESSOR-6 HANDBOOK

# F-65 CHANGE NOTICE NO.1

# F-65 CHANGE NOTICE

No. 1 Sept 1964

#### PROTECTION AND RELOCATION

The following description modifies and amplifies several partions of this handbook, primarily the section called Memory Protection on page 46.

The purpose of the protection and relocation hardware on the PDP-6 is to make it possible to run a completely undebugged program in any part of memory, without its affecting any other part of memory, any I/O device, or the continued operation of the computer.

Relocation is a means by which a program written to run, say, from locations 0-3777 can actually be run in locations 1 2000-15777, or in any other block of 4000 contiguous registers, starting at an integral multiple of 2000. (All numbers in this change notice are octal.) Another constraint on relocation is that the program must be able to be moved to some other location at any time, without affecting its operation in any way. In particular, operation of the program must not be dependent on its actual location memory. The relocation hardware should not affect references to the accumulator/index register area, so that time savings gained through use of the fast memory are not compromised. Lastly, since the relocation hardware must do its work before any memory reference is allowed, it should be as fast as possible.

The protection logic comes in two parts: memory protection and illegal instruction protection. The memory protection allows a program to use any integral number of 2000-word blocks. This logic works simultaneously with the relocation logic so as to determine whether an address is valid before going to the memory system. The illegal instruction protection suppresses any I/O instructions or an attempt to halt the machine by means of JRST 4. In addition JRST 10, which affects the interrupt system, is suppressed. All of these instructions, plus the programmed operator group, are arranged to trap to the executive routine which can take any action it pleases.

#### Programming

PDP-6 can operate in two modes: executive, in which all instructions are legal, and no relocation or protection is in effect; and user mode, in which the protection and relocation are effective. The machine is reset to the executive mode by the I/O RESET key, or when power is turned on. If the machine is in the executive mode, the CPA EXEC indicator on the upper left hand indicator panel will be on. This bit may be tested by looking at bit 5 of the word stored by JSR, etc. If in user mode, this bit will be 1. Also, a CONI to the arithmetic processor will have a 1 in bit 21 in the executive mode.

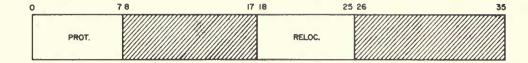

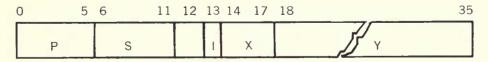

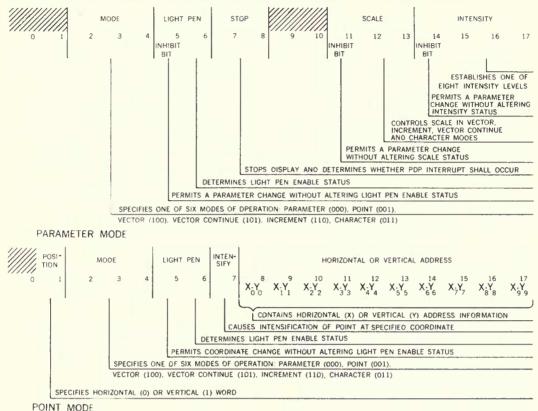

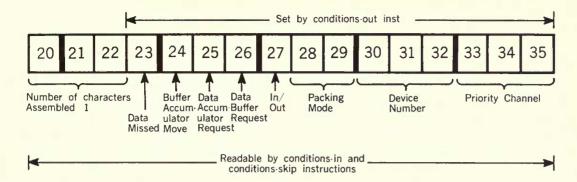

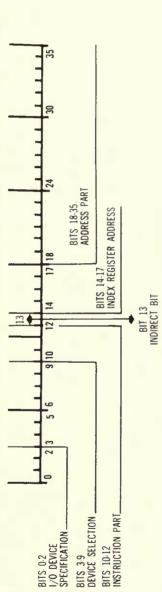

The relocation and protection registers are loaded by a DATAO to the arithmetic processor (device 0). The data word should have the format shown below:

The protection register should be loaded with the largest allowable address to which the user may make reference. In other words, if any effective address used for memory reference given by the user is greater than the number in the protection register, with ten ones to the right, a violation has occurred. The relocation register is loaded with the address which is to be added to the effective address specified by the programmer. Note that the protection is performed on the unrelocated address. Furthermore, relocation is performed only on addresses used to reference memory. For example, if the word addressed by the DATAO contained 006000004000, the following table would apply:

| Effective<br>Address | Protection<br>Violation | Relocated<br>Address |

|----------------------|-------------------------|----------------------|

| 000100               | no                      | 004100               |

| 006000               | no                      | 01 2000              |

| 007777               | no                      | 013777               |

| 01 0000              | yes                     |                      |

| 000012               | no                      | 000012               |

In the event of a memory protection violation, the Illegal Memory Address flag is set, which causes an interrupt on whatever channel the APR is assigned. This is bit 22 in the APR status register. A CONO with bit 22 turns off this bit. On present machines, the indicator for this bit is labeled CPA ILL OP. Note that the program counter may or may not have been advanced past the offending instruction, depending on which reference was illegal.

When a program interrupt occurs, for this or any other reason, relocation is suspended. The executive mode is only entered if a JSR instruction is given at the interrupt location, either in 40 + 2i or in 41 + 2i as the consequence of a BLKI or BLKO overflow. It is important to note that BLKI, BLKO, and JSR are the only valid interrupt instructions. JSR stores the state of the executive/user mode, as explained previously. When the interrupt is dismissed, with a JRST 12, RETURN, the channel is reset, and if MB5 of the indirect location word was on, the user mode is re-entered for the next instruction.

The illegal instruction protection uses the programmed operator trap mechanism. When in user mode, any IOT, programmed operator, or JRST with bits 9 or 10 equal to 1, causes the instruction to be deposited in non-relocated location 40, and location 41 to be executed. For proper operation, the instruction in 41 must be a JSR. Although these

illegal instructions themselves do not increment the program counter, the JSR nevertheless stores the location of the offending instruction plus one. Since the effective address has already been calculated, bits 13–17 of location 40 are 0, and bits 18–35 have the effective address. The state of the user mode is stored by the JSR, as in a normal interrupt, and can be restored by the same means.

#### LINE PRINTER TYPE 646

The following description replaces the three paragraphs on page 61, starting just below the diagram.

PDP-6 will transfer five 7-bit ASCII-coded characters in bits 0-34 to the buffer register of the Type 646. Each character, starting with the left most, is processed in turn. Printable characters are sent out one at a time, directly to the printer. Control characters are decoded within the interface and functions associated with each character are initiated by signals that are sent to the printer. Illegal or unassigned control characters are ignored.

The printer loads characters at a 10-microsecond rate, moves paper at the rate of one line per 18 milliseconds and clears out the buffer memory in 3 to 6 milliseconds.

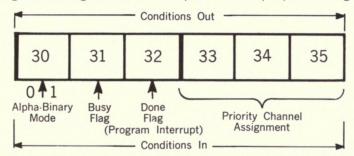

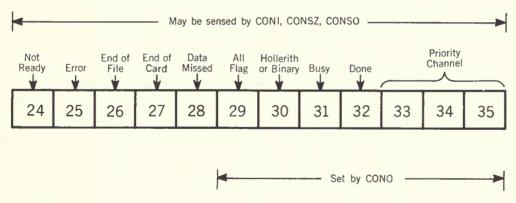

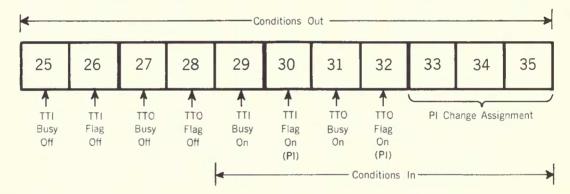

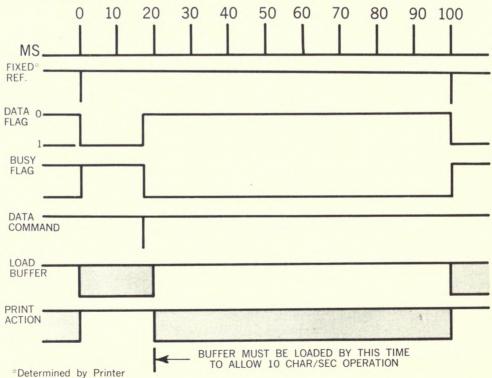

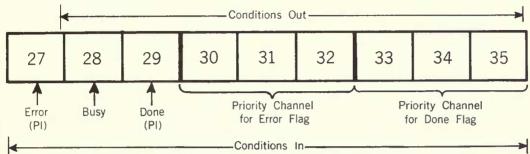

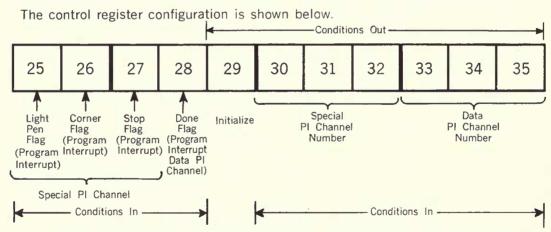

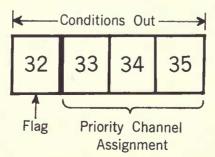

Conditions out with bit 25 a 1, clears the interface and initiates the printer buffer clearing operation. The Busy flag within the interface is set and the Done flag is reset. When the printer has completed its clearing operation, the Done flag is set, and the Busy reset. The Done interrupt is also generated when the flag is set.

Conditions out always sets the priority levels for the Done and Error interrupts. Bits 33, 34, and 35 determine the Done priority level and bits 30, 31, and 32 determine the Error priority level. The Error interrupt is caused by the printer going off-line, by removing the cable connection between the printer and the 646 control, or by over-filling the printer buffer with more than 120 characters.

The Data out instruction loads five characters into the interface and initiates the processing of the first character. The Busy is set and the Done reset at this time. After the fifth character has been processed, the Busy will be reset and the Done set.

The following remarks should be added to the end of the Line Printer section on page 62.

If the program attempts to transmit more than 120 printable characters to the printer, the Line Overflow interrupt and status level occurs after the 121st character is transmitted. The Done flag will never be set. To return to normal operation, send a Carriage Return control character with a data out instruction or perform a conditions out instruction to clear the control unit and printer.

The Start-Stop push button switches on the printer console put the printer in the on-line or off-line condition. Once the printer has been placed on-line with the computer, and characters have been loaded into the printer buffer, the printer will not go off-line,

even though the stop button has been pushed, intil the stored characters have been printed out. If the Stop button is operated and the program fails to print out the stored characters, both the Start and Stop switch indicators will be lit.

A Print button, which will enable the generation of a Print pulse when this condition occurs, will be added to the printer console in the near future.

#### COMPREHENSIVE LIST OF CHANGES

The following list of changes results from the engineering design changes described above, from errors made in the production of this handbook, and from the following: Memory skip instructions have been changed to store results in an accumulator; some of the jump instructions have been changed to store the processor flags.

| Page   | Location                                      | Change                                                                                                                          |

|--------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 21     | Second sentence under<br>Programmed Operators | Replace with: When used, bits 0-12 of the instruction are stored in bits 0-12 of location 40; bits 13-17 are cleared.           |

| 32     | 7th item in table                             | Change OR to XOR.                                                                                                               |

| 32     | 8th item in table                             | Change IOR to OR.                                                                                                               |

| 33     | 3rd paragraph, second sentence                | Replace with: If a combined shift instruction, and the specified accumulator is 178, then location 0 is taken to be AC+1.       |

| 33     | Last paragraph                                | Add: If an accumulator, other than zero, is specified in a Memory Skip instruction, the result is loaded into the specified AC. |

| 36     | JSP                                           | Add: This instruction stores flags in the same manner as the JSR.                                                               |

| 37     | PUSHJ                                         | Add: This instruction stores flags in the same manner as the JSR.                                                               |

| 38     | CONSZ and CONSO                               | Delete "contents of" before "effective address." These instructions use the effective address itself as a mask.                 |

| 40     | 8th line from top                             | Change Illegal Instruction to Memory Protection.                                                                                |

| 40     | CONI, bit 22                                  | Change Illegal Instruction to Memory Protection.                                                                                |

| 42, 43 | Four programming ex-<br>amples                | Delete all commas preceding MNE.                                                                                                |

| Page | Location                                    | Change                                                                                                                                            |

|------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

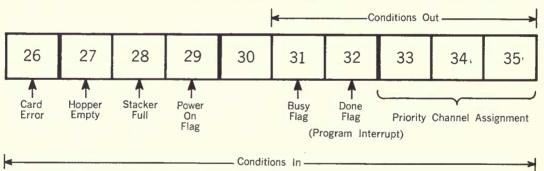

| 54   | Bit 29 in top diagram                       | Add: Power On.                                                                                                                                    |

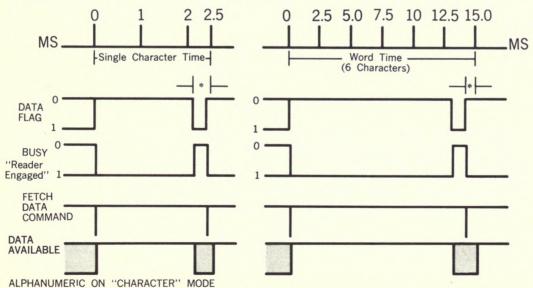

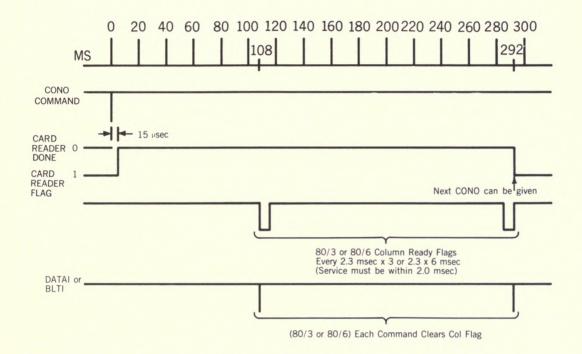

| 57   | Before timing diagram                       | Add: If the reader is not ready when<br>the busy flag is set, the command<br>will be 'stored' and executed when<br>the card reader becomes ready. |

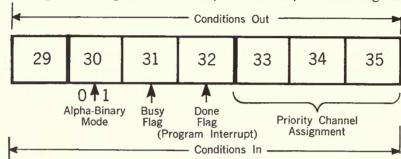

| 58   | Bits 33, 34, and 35 of<br>the lower diagram | Change PI Change Assignment to PI Channel Assignment.                                                                                             |

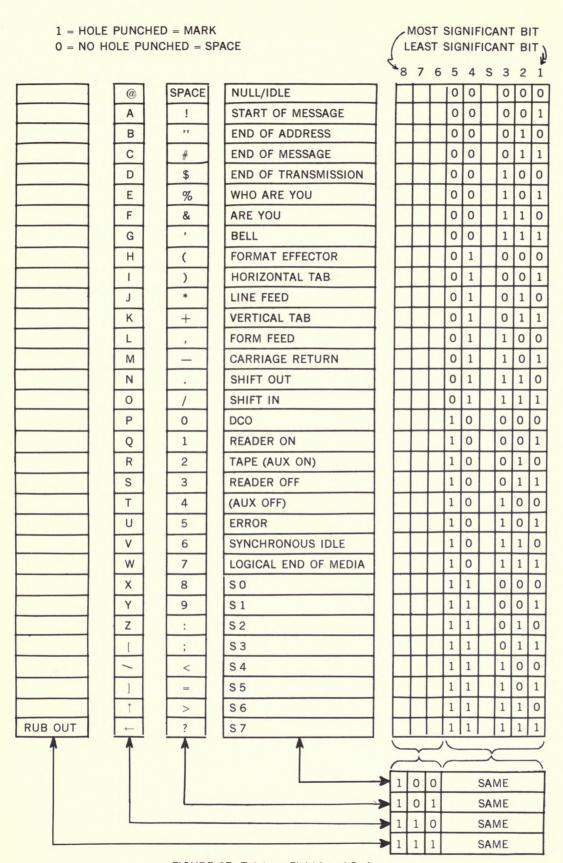

| 59   | Second space above RUB<br>OUT               | Add: ALT MODE                                                                                                                                     |

|      | Third space above RUB<br>OUT                | Add: ACK                                                                                                                                          |

| 61   | EOT (004)                                   | Add: Any characters located to the right of the EOT character within the 35 bit word will be lost.                                                |

| 61   | Diagram                                     | Add: Bit 25 Clear, bit 26 Line Overflow Error.                                                                                                    |

| 62   | Three paragraphs following the diagram      | Replace with: The new material given above in this change notice.                                                                                 |

|      | Last column of table                        | Replace with: Skips to top of page 30 2 3 6 10 20 1                                                                                               |

| 62   | End of the Line Printer section             | Add: The new material given above in this change notice.                                                                                          |

| 80   | Diagram                                     | Add: Add bit 31 and label it Reset to Zero. Replace Flag with Release.                                                                            |

| 83   | Second line under 4                         | Delete: in-out register                                                                                                                           |

| 83   | Third line under 4                          | Delete the sentence beginning: In some Type 633 models                                                                                            |

| 84   | Second line                                 | Delete: in-out register                                                                                                                           |

| 84   | Third line                                  | Delete sentence beginning: In some Type 633 models———— to end of paragraph.                                                                       |

| 90   | FDV, Comments column                        | Change left-adjusted to right-ad-<br>justed                                                                                                       |

| Page           | Location                      | Change                                                                       |

|----------------|-------------------------------|------------------------------------------------------------------------------|

| 91             | FDVR, Comments column         | Change left-adjusted to right-ad-<br>justed                                  |

| 93             | SKIP, Comments column         | Add: Results to accumulator if an accumulator other than 0 is specified      |

| 94             | AOS, Comments column          | Add: Same comment.                                                           |

| 95             | SOS, Comments column          | Add: Same comment.                                                           |

| 98             | PUSHJ, Comments column        | Add: Stores flags in same manner as JSR.                                     |

| 99             | JSP, Comments column          | Add: Stores flags in same monner as JSR.                                     |

| I–O<br>Summary | 166 Central Processor         | Device/Speed column: Replace (CPA) with (APR)                                |

| Chart          |                               | Bit 18: Replace PDL OV FLAG with CLEAR PDL OV FLAG.                          |

|                |                               | Bit 19: Replace I/O RESET with PD OV FLAG (red) and I/O RESET (green)        |

|                |                               | Bit 21: Add USER MODE FLAG (red)                                             |

|                | 760 Perforated Tape<br>Reader | Bit 29: Should be red                                                        |

|                | 646, 680 Line Printer         | Bit 25: Add CLEAR                                                            |

|                | 630 Line Counter              | Bits 33-35: Replace PRIORITY IN-<br>TERRUPT ASSIGNMENT with LINE<br>COUNTER. |

# DATA COMMUNICATIONS SYSTEM TYPE 630

The diagram below should replace the corresponding portion of the Input-Output Summary Chart inside the back cover.

|                                                          | OP   | ٦,  | 30    | 31              | 32                   | 33                            | 34             | 35     | INPUT<br>BITS | OATA I                                                                                               |

|----------------------------------------------------------|------|-----|-------|-----------------|----------------------|-------------------------------|----------------|--------|---------------|------------------------------------------------------------------------------------------------------|

|                                                          | CODE | L,  | 30 31 | 35 34           | 34                   | 33                            | OUTPUT<br>BITS | CATA O |               |                                                                                                      |

| 630 DATA<br>COMMUNICATION<br>SYSTEM (DCS)<br>HALF DUPLEX | 300  |     |       |                 | SCANNER<br>FLAG      | LAG BITS 33-35                |                |        | 8             | SCANNER SPECIFIES STATION     INPUT A CHARACTER     CLEAR STATION FLAG                               |

|                                                          | DCSA | ,,  |       | STATION<br>ZERO | RELEASE<br>SCANNER   | PRIORITY INTERRUPT ASSIGNMENT |                |        | 6             | BUFFER SPECIFIES STATION     COUTPUT A CHARACTER     CLEAR STATION FLAG                              |

|                                                          | 304  | ,,, |       |                 | ON NUMBE             |                               |                |        | 8             | 1. SCANNER SPECIFIES STATION<br>2. INPUT A CHARACTER<br>3. CLEAR STATION FLAG<br>4. RELEASE SCANNER  |

|                                                          | OCSB |     |       |                 | N NUMBER<br>SENO BUF |                               | ı              |        | Ð             | 1. SCANNER SPECIFIES STATION<br>2. OUTPUT A CHARACTER<br>3. CLEAR STATION FLAG<br>4. RELEASE SCANNER |

# PROGRAMMED DATA PROCESSOR-6 HANDBOOK

# PROGRAMMED DATA PROCESSOR - 6

36-bit word length  $\blacksquare$  15 index registers and/or accumulators FORTRAN II — MACRO-6 assembler — utility programming library Integrated hardware and software for time sharing  $\blacksquare$  Microtape Asynchronous operation, modular construction  $\blacksquare$  Memory overlap Core memories up to 262,144 words, 2  $\mu$ sec, directly addressable Fast memory 16 words, 0.4 microsecond  $\blacksquare$  128 input-output devices 363 instructions  $\blacksquare$  fast floating point — multiply 14  $\mu$ sec average Program assignable operation codes  $\blacksquare$  Byte manipulation, half word Block transmission  $\blacksquare$  Seven channel priority interrupt system Programmed input-output transfers require no data channels Multiple processors  $\blacksquare$  Remote input-output  $\blacksquare$  Mass memory

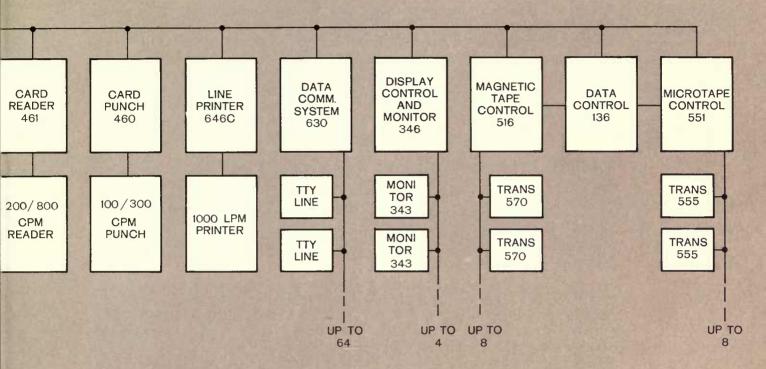

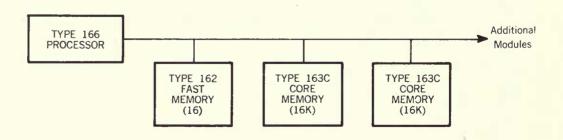

Figure 1 Typical PDP-6 System

# CONTENTS

CHAPTER 1

PDP-6 SYSTEM DESCRIPTION

|                                                 | Page  |

|-------------------------------------------------|-------|

| Processors                                      |       |

| Input/Output                                    |       |

| Memory                                          |       |

| The Supervisory Control Program                 |       |

| System Programs                                 |       |

| Input/Output Equipment                          |       |

|                                                 | ., ., |

|                                                 |       |

| CHAPTER 2                                       |       |

| ARITHMETIC PROCESSOR TYPE 166                   |       |

| Processor Registers                             | 15    |

| Console Controls and Indicators                 |       |

| Programming for Type 166 Processor              |       |

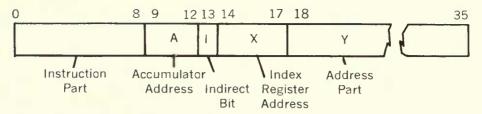

| Instruction Word Format                         |       |

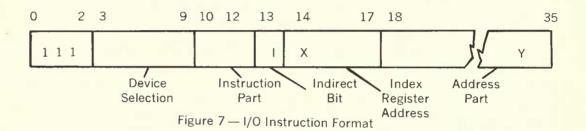

| Effective Address Calculation                   |       |

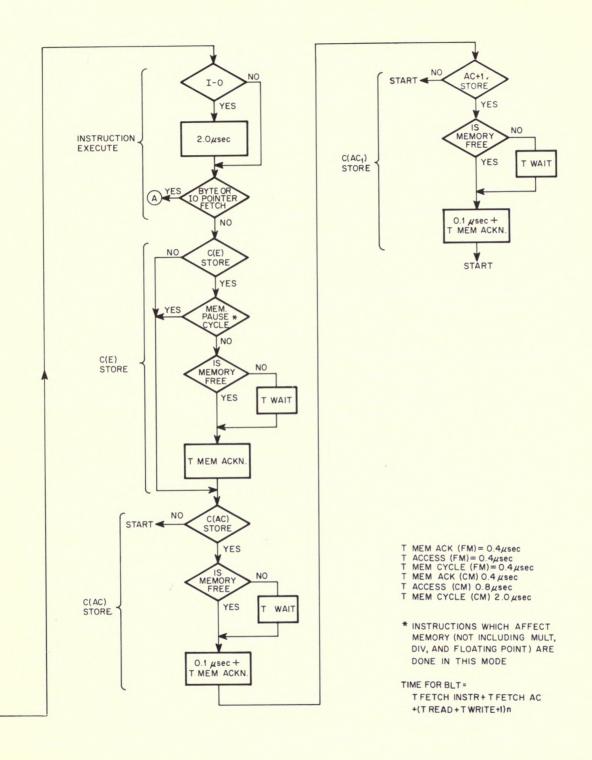

| Timing                                          |       |

| Instruction Classes                             |       |

| Data Transmission                               |       |

| Arithmetic and Logical Executive                |       |

| Jump Instructions                               |       |

| Push Down Instructions                          |       |

| Input-Output Instructions                       |       |

| Input-Output Programming for Type 166 Processor |       |

| Processor                                       | 39    |

| Priority Interrupt System                       |       |

| Input-Output Programming                        | 41    |

|                                                 |       |

|                                                 |       |

| CHAPTER 3                                       |       |

| MEMORY                                          |       |

| Memory Functions                                |       |

| Address Selection                               |       |

| Memory Overlapping                              |       |

| Memory Protection                               |       |

| Memory Timing                                   |       |

| Memory Module Type 163                          | 48    |

| Memory Module Type 162                          |       |

| Execution Times                                 |       |

|                                                 |       |

# CHAPTER 4 INPUT-OUTPUT

|          |      |                                                     | Page |

|----------|------|-----------------------------------------------------|------|

| Priority | Inte | rrupt System                                        | 51   |

|          |      | t Devices                                           |      |

|          |      | d Tape Punch Type 761                               |      |

|          |      | d Tape Reader Type 760                              |      |

|          |      | ch Control Type 460                                 |      |

|          |      | der Type 461                                        |      |

|          |      | er Type 626                                         |      |

|          |      | ters Type 646 and 680                               |      |

|          |      | tal CRT Display Type 346                            |      |

|          |      | trol Type 136                                       |      |

|          |      | e                                                   |      |

|          |      | Tape Control Type 516                               |      |

|          |      | nmunication System Type 630                         |      |

| APPEN    | DIX  | 1, INSTRUCTIONS                                     | 85   |

|          |      | 2, CODES                                            |      |

| APPEN    | DIX  | 3, GLOSSARY OF ABBREVIATIONS                        | 109  |

|          |      |                                                     |      |

|          |      |                                                     |      |

|          |      | ULLICTRATIONS                                       |      |

|          |      | ILLUSTRATIONS                                       |      |

| Figure   |      | Typical PDP-6 System                                |      |

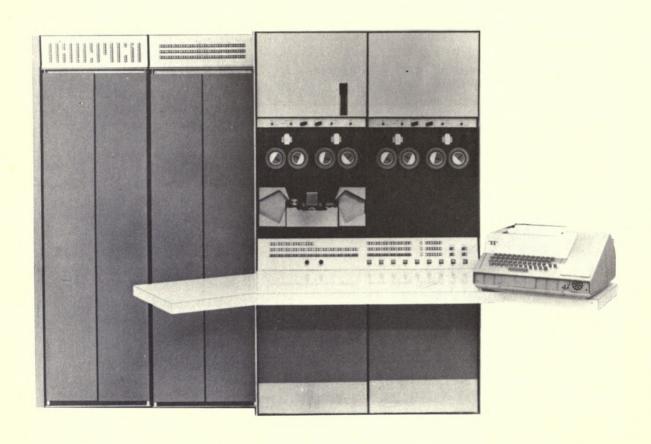

| Figure   |      | Arithmetic Processor Type 166                       |      |

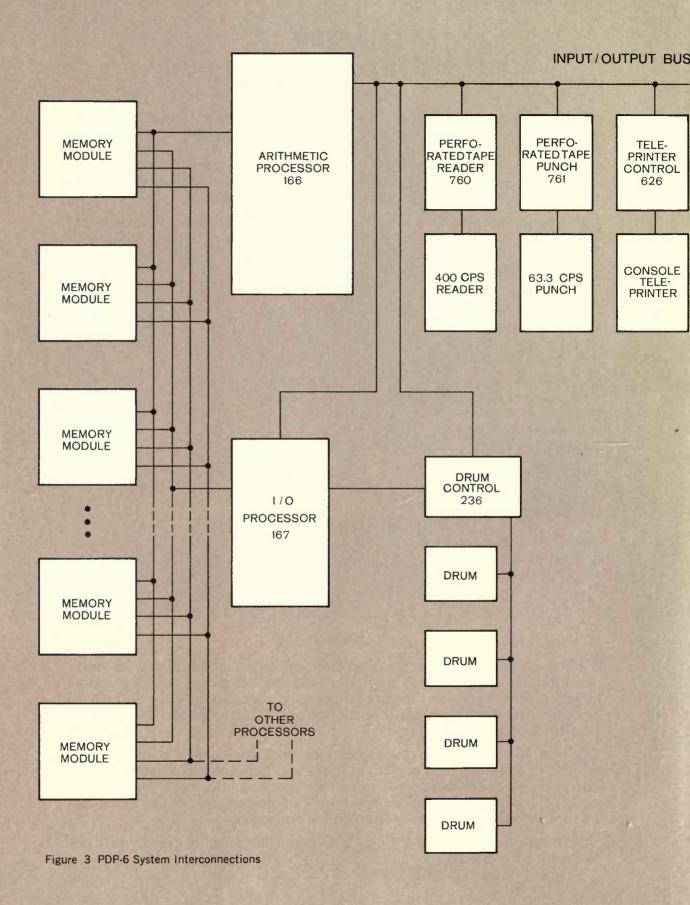

| Figure   |      | PDP-6 System Interconnections                       |      |

| Figure   |      | Data Flow Diagram                                   |      |

| Figure   |      | The Control Panel                                   |      |

| Figure   |      | Basic Instruction Format                            |      |

| Figure   |      | I/O Instruction Format                              |      |

| Figure   |      | Instruction Time Flow Diagram                       |      |

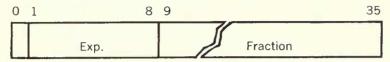

| Figure   |      | Byte Pointer Format                                 |      |

| Figure   |      | Floating Point Format                               |      |

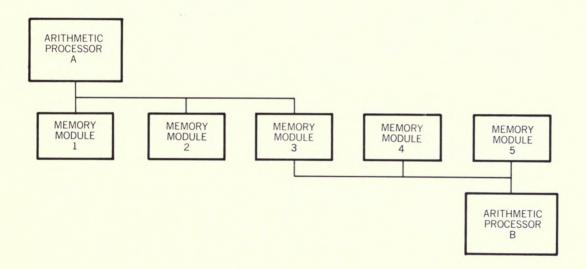

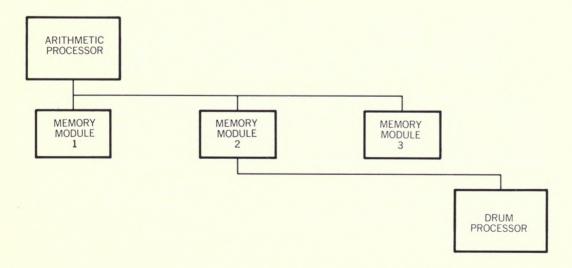

| Figure   |      | Typical Memory System                               |      |

| Figure   |      | Partial Memory Sharing by Two Arithmetic Processors |      |

| Figure   |      | Use of Backup Storage in Time-Sharing Operations    |      |

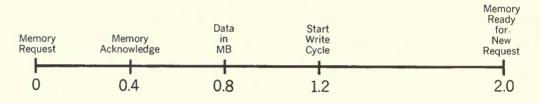

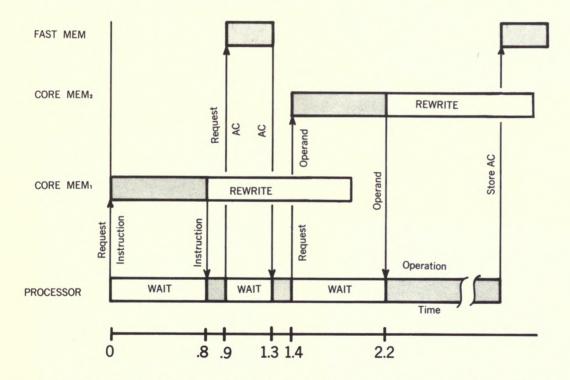

| Figure   |      | Type 163 Core Memory Internal Timing                | 48   |

| Figure   | 15   | Typical Memory Timing Using Three Memory            |      |

| F:       | 1.0  | Modules in the Execution of One Instruction         |      |

| Figure   |      | Card Reader Codes                                   |      |

| Figure   |      | Teletype Eight Level Code                           |      |

| Figure   |      | Data Control Type 136                               | 66   |

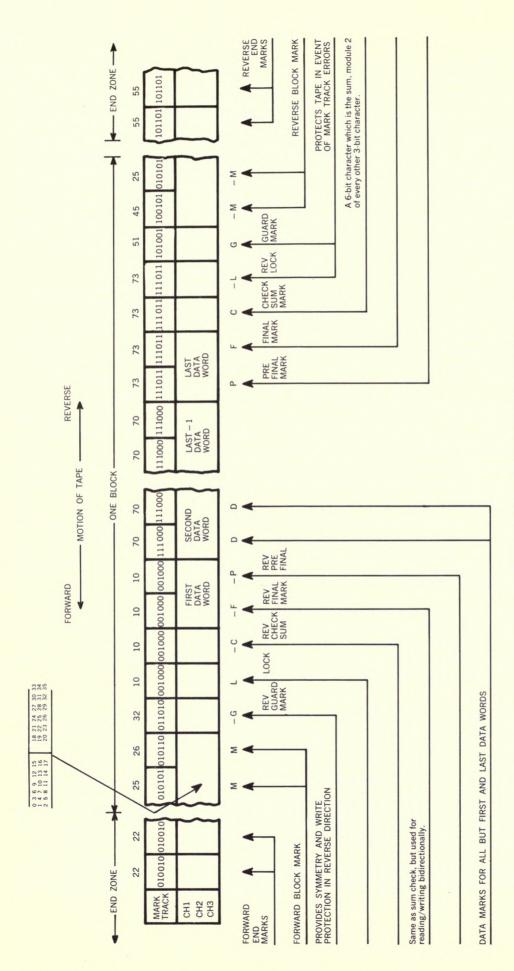

| Figure   |      | Mark and Information Track Formats                  |      |

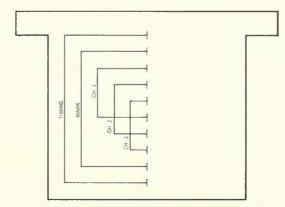

| Figure   |      | Placement of Microtape Tracks                       |      |

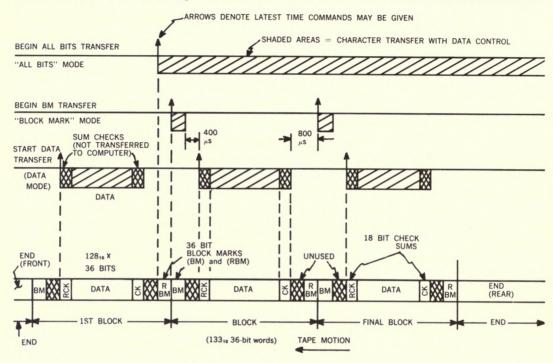

| Figure   |      | Microtape Format                                    |      |

| Figure   |      | Microtape Control                                   |      |

| Figure   |      | Pooled Transports                                   | 78   |

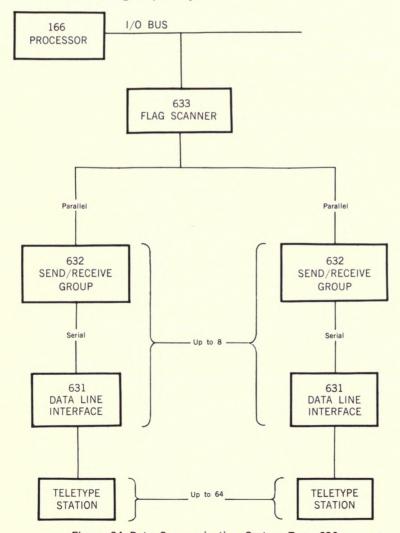

| Figure   | 24   | Data Communication System Type 630                  | 83   |

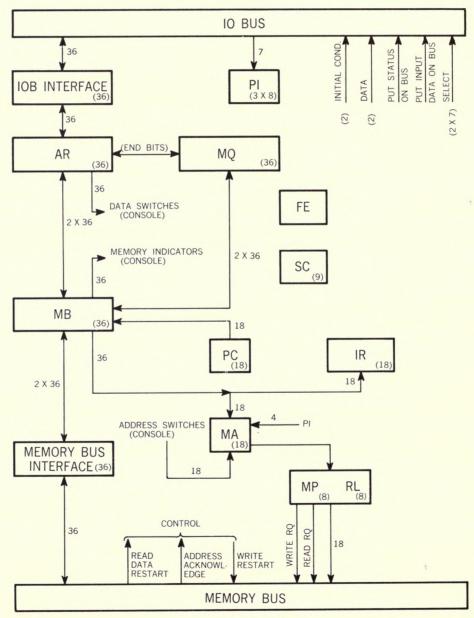

Figure 2 Arithmetic Processor Type 166

# CHAPTER 1 PDP-6 SYSTEM DESCRIPTION

Programmed Data Processor-6 (PDP-6) is a general-purpose digital computing system designed for scientific data processing. The flexibility of this system permits the user to specify the data handling capacity and the exact configuration needed to meet his requirements. The system can be expanded with presently available equipment or, at a later date, with equipment yet to be developed. Faster memories, for example, can be added as they become available.

PDP-6 design eliminates the need for off-line conversion equipment. Conversion of programs from cards or paper tape to magnetic tape can be done concurrent with normal program running. Users at peripheral teleprinters can simultaneously prepare and debug their programs on line.

The PDP-6 system consists of processors, memories, and input/output devices. Since each is autonomous (no device is dependent upon another for its timing), a system configuration can include memory modules of different speeds, processors of different types sharing the same memory modules, and standard or unique input/output devices.

For maximum flexibility of system configurations, the PDP-6 system is built around two busses: processor-memory bus and processor-input/output bus. The memory bus permits each processor to directly address 262,144 words of core memory, automatically permits overlapping, and simplifies multiprocessor operation. An input/output bus of a processor can service up to 128 devices.

The operating system consists of a supervisory control program, system programs, and system subroutines. Included are a Symbolic Assembler and Macro Processor, a FORTRAN II Compiler, and debugging aids. A library of general utility programs is also provided.

Neither the processors nor any of the standard peripheral equipment require an air-conditioned environment or floor reinforcement. Ordinary 115-volt power is sufficient for all equipment.

## **Processors**

A PDP-6 system can include any number of processors of the same or different types. The Type 166 is a 36-bit arithmetic processor with many powerful features, including 16 accumulators, 15 index registers, built-in floating point arithmetic, and byte operations capability. Memory protection and relocation registers are included for time-sharing operations.

The Type 167 I/O Processor gives direct memory access to high speed devices, such as drums, discs, and displays. It takes over local control of data transfers after receiving system commands and initial conditions from the arithmetic processor. Thereafter the two processors operate asynchronously, so that I/O transfers are carried out in parallel with arithmetic processing.

Up to three controls, such as the Type 236 Drum Control, can be connected to the Type 167 I/O Processor.

# PDP-6 — A MODULAR SYSTEM

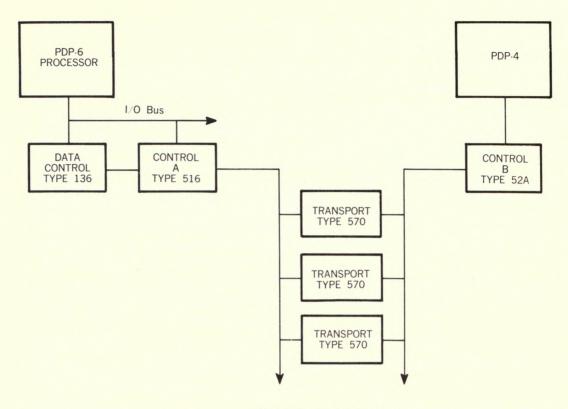

The diagram shows the three main parts of a PDP-6 system, memories, processors, and input/output equipment, interconnected with busses. Memories and input/output devices contain their own buffer registers and control circuits, including decoders to recognize commands from the processors. The Data Control Type 136 is a double-buffered device which is used not only with magnetic tape equipment, as shown here, but with any high speed, block transfer device, such as drum or disc.

The system shown in this diagram is a theoretical one of very high capacity, but it is entirely within the capability of PDP-6. Memory size, indicated by the modules on the left, can be as large as 262,144 words per processor, and up to four processors can address a given memory module. Very high speed devices, such as drum, tape, disc, and display, can have direct access to the

memory system through the I/O Processor Type 167. The combination of the asynchronous nature of the system and the characteristics of the memory bus makes possible truly simultaneous memory references by two or more processors. Sequential memory references made by one processor can be overlapped.

PDP-6 is also a highly effective system in a minimum configuration. All system programs will operate in a system consisting of a Type 166 Arithmetic Processor, a memory module of 16,384 words, a Microtape system, and a teleprinter. Later expansion of either the memory or input/output system can be made with no change whatever in the existing system. Memory modules can be of any speed: A low cost system might call initially for slower (5-microsecond) memories, later to be augmented by faster memories (down to 0.5-microsecond).

PDP-6 systems are thus completely adaptable to current and future requirements, both technical and budgetary.

# Input/Output

The input/output bus consists of device selection, data, control, and status sense lines. A 7-channel program-assignable priority interrupt system signals the processor when input/output devices require service. Word count and memory address registers are located in the processor and are available to all devices. This reduces the cost of various input/output controls, and permits data block transfers between tapes, card readers, printers, displays, and other devices.

# Memory

The PDP-6 core memory subsystem permits modular expansion using blocks of different sizes and speeds. The types 163B and 163C core memory modules contain 8,192 and 16,384 words, respectively. Each has a word length of 36 bits, a cycle time of 2 microseconds, and an access time of 0.8 microseconds. The Type 162 Fast Memory Module contains 16 words with a 0.4-microsecond cycle. Slower core memories, such as the 5-microsecond Type 161, can be used where economy is an overriding criterion.

The memory-processor bus permits memory cycle overlap, gives all processors direct access to memory, and permits easy expansion and modification of the memory subsystem. In addition, the bus allows the processors to remain connected to memory only as long as needed to transfer information: That is, a processor can put a word on the bus and resume operations as soon as the memory acknowledges, without waiting for the memory to store the word. Similarly, when reading a word out of memory, the processor takes the information and operates on it immediately, without waiting for the memory to finish the rewrite portion of its cycle.

Maximum system efficiency is achieved when sequential memory references address alternate memory modules. The addressed module places data on the bus as soon as it is available in the memory buffer and disconnects itself from the bus while rewriting, freeing the processor to store the result or seek the next instruction in a second memory module before the first one has completed rewriting. Utilizing such overlapping memory references, PDP-6 users can effectively cut in half the time required for average random accesses. Multiple connections between the bus and each memory module permit module sharing on a priority basis for multi-processor operations.

## PROGRAMMING SYSTEM

The programming system for PDP-6 consists of a supervisory control program, system programs, and library routines. The entire system is designed to run on any PDP-6 system with at least 16,384 words of core memory, a console teleprinter, and a Microtape system. However, the programming system is modular. Parts of it can run on machines with smaller memory capacities. For example, programs can be assembled with MACRO6 using the above-mentioned input/output equipment and only 8,192 words of core memory.

A variety of programs are provided through the Digital program library, and a continuous in-house program design effort regularly improves and expands the library.

# The Supervisory Control Program

This is the name given to a collection of programs remaining permanently in memory to provide overall coordination and control of the total operating system. The segments of the program are:

COMMAND CONTROL PROGRAM handles all commands addressed to the system from the user-consoles. These commands would include requests to log in or out, a request to use the edit program, requests to have a program placed on the run queue, requests to load a program, etc.

PROGRAM SCHEDULER is called at regular intervals to decide which program in memory is to be run. A running program is temporarily terminated each time its allotted time has run out or when it requires input/output operations with a device that is busy. A program may be terminated temporarily by user intervention to the scheduler, or it may suspend its own operation. Temporary termination does not remove the program from memory. A program may be dumped on backing storage and permanently discontinued by calling the scheduler and allocator.

FACILITIES ALLOCATOR is called any time an I/O device or memory space is required. It may be called from a user-console or by a running program. Under this program one user-console is designated the operator console. As such it has special facilities available which are not available to other consoles, such as line printer assignments. Storage is permanently assigned for all resident programs, that is, those programs that are in memory at all times. Finally, "logical" tape assignments are made. Two Microtape units are designated the system library and the system scratch tape. Two other tapes may be assigned as peripheral input tape, used to prepare jobs to be stacked from cards or paper tape, and system input tape, used to input a full tape. (Each user-console may require a Microtape unless programs requiring files are to be run.)

COMMAND DECODER preprocesses commands from the user-console. This program is used to convert parameters, etc., before the command is sent to the program for which the command is intended.

I/O CONTROL is called whenever an I/O device is to be used. This program assigns equipment, controls the I/O devices, controls data transfers between memory and the I/O device, and controls the buffering of data for the device. (Users provide the necessary buffering for devices which require file buffering.) All program I/O instructions are trapped, and the actual control of the I/O operation then passes to the I/O Control Program.

# System Programs

These are the programs designed to implement system functions which may be requested from the user-console. This is in contrast to system subroutines which may be called by system programs or other programs. System programs are normally provided by Digital, but they may be provided by each installation for its users. The programs contain a mode by which they may be terminated to return the communication link to the system. Some of the system programs are described below.

Can we get io Ban io trap register that allows certain io references in user mode EDITOR PROGRAM manipulates the text of a named file on a Microtape or in the user area of the drum (corresponding to Microtape). This file may be used for the creation of text or for later use as data or as a program to be translated by the FORTRAN Compiler, etc. The commands provided for the editor allow text to be created, deleted, or moved about.

PERIPHERAL CONVERSION PROGRAM handles all those jobs normally done by a separate peripheral processor. The priority interrupt system and multiple memory accumulators in the PDP-6 eliminate virtually all loss in running time. Such processing is done through the arithmetic processor.

INTER-CONSOLE MESSAGE PROGRAM switches message traffic between the various user-consoles. This program allows the user to request manual operations by the operator and receive acknowledgment. Such an operation would be the mounting/dismounting of user tapes.

LINKING LOADER PROGRAM accepts programs in a form produced by the translators, and produces an area of core memory loaded with the program. Upon request, it may also produce a storage map of the loaded programs along with symbol tables. Several programs may be linked together in loading. The loader requests special library tapes to be loaded, and verifies that the program has been completely loaded.

TRANSLATOR DISPATCHER is called to load the FORTRAN, MACRO6, or other translators. The translators are rather large programs that do not reside in memory, but are stored on the System Library tape until they are called into memory by the translator.

FORTRAN II COMPILER accepts FORTRAN II input statements and produces relocatable binary output coding for later loading by the Linking Loader. Compiling is done in one pass. PDP-6 FORTRAN II is an extension of the conventional FORTRAN II language to give the user more facilities and to take advantage of PDP-6 hardware. The ASCII character set is used. Subscripts may consist of statements (fixed or floating). Any number of dimensions may be used to specify an array. Signed integers have 36-bit values, but when used as subscripts are truncated to 18 bits.

MACRO6 ASSEMBLY PROGRAM translates MACRO6 input language to a relocatable binary output for the Linking Loader. MACRO6 is a two-pass assembly program, and the language provides for macro instruction definitions and usage. Literal assignments are made by brackets []. Numbers may be expressed as binary, octal, decimal, and floating point. Text may be placed in a binary program by the occurrence of the "text" data generating statement, and "byte" causes a string of bytes to be assigned and packed into a word. The "repeat" control statement causes the statements following the control to be repeated "n" times.

DEBUGGING PROGRAM (DDT) is loaded with a program and allows all assembly language programs to be debugged. The program may be started or stopped, words in the program may be modified, and DDT may search the program looking for particular words. DDT may also be used in a "trace" or break point mode, and the program is run until a particular location (a break point) is encountered.

#### THE SYSTEM SUBROUTINES include:

1. I/O Format Control which provides for the various format statements used in the FORTRAN II language. These subroutines are also available to other programs and may be called from the systems library tape. 2. Arithmetic Subroutines which include all the arithmetic subroutines required for FORTRAN II, such as, sine, cosine,  $log_{E}$ ,  $log_{10}$ , exponent, tangent, arctangent, and square root.

# INPUT/OUTPUT EQUIPMENT

Digital offers a large selection of optional equipment for full utilization of the extensive input/output capacity of the system.

#### MICROTAPE TRANSPORT TYPE 555

A fixed-address magnetic-tape facility for high speed loading, readout, and on-line program debugging. Read, write, or search speed is 80 inches a second. Density is 375 bits an inch. Total storage is three million bits. Features phase recording, rather than amplitude recording; redundant, nonadjacent data tracks; and a pre-recorded timing and mark track.

#### MICROTAPE CONTROL TYPE 551

Controls up to eight Type 555 Microtape Transports. Searches in either direction for specified block numbers, then reads or writes data. Uses the Type 136 Data Control to assemble data and buffer transfers to the processor.

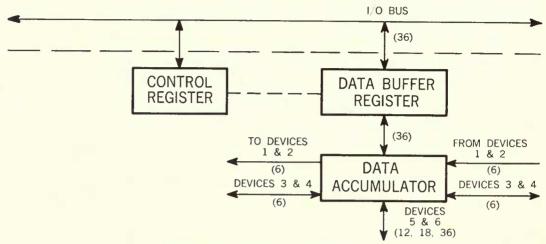

#### DATA CONTROL TYPE 136

Provides for assembly of 6, 12, 18, or 36-bit characters; six input/output devices can be controlled.

#### TELEPRINTER AND CONTROL TYPE 626

Permits on-line programming and debugging. Provides hardcopy outputs. Is standard Teletype equipment, operating at ten characters a second.

#### TELEPRINTER INTERFACE TYPE 630

Automatically scans up to 64 teleprinter (TTY) lines. Signals a program interrupt when teleprinter needs service.

#### CARD PUNCH CONTROL TYPE 460

Permits on-line punching of cards in any format, including IBM, at 100 or 300 cards a minute.

#### CARD READER AND CONTROL TYPE 461

Provides on-line reading of standard punched cards at 200 or 800 cards a minute in alphanumeric or binary codes.

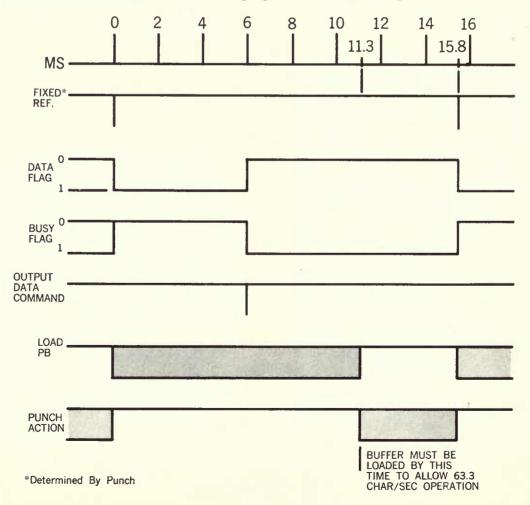

HIGH SPEED PERFORATED TAPE PUNCH AND CONTROL TYPE 761 Punches 8-hole tape at 63.3 characters a second.

HIGH SPEED PERFORATED TAPE READER AND CONTROL TYPE 760 Reads perforated paper tape photoelectrically at 400 characters a second.

#### MAGNETIC TAPE CONTROL TYPE 516

Automatically controls up to eight tape transports Type 570 or IBM 729 series. Permits reading, writing, forward/backward spacing, rewind and unload, and rewind. Uses a Type 136 Data Control to assemble data and buffer transfers to the processor. Longitudinal and lateral parity are checked.

#### MAGNETIC TAPE TRANSPORT TYPE 570

Tape motion is controlled by pneumatic capstans and brakes, eliminating conventional pinch rollers, clamps, and mechanical arms. Tape speed is either 75 or 112.5 inches a second. Track density, program-selectable, is 200, 556, and 800

bits per inch. Tape width is one-half inch, with six data tracks and one for parity. Format is compatible with IBM NRZI. Dual heads permit read checking while writing.

#### I/O PROCESSOR TYPE 167

Establishes a data transmission path between main memory and the drum(s). Up to four drums can be connected to the I/O processor.

#### MAGNETIC DRUM AND CONTROL TYPE 236

Drum stores 1,048,576 36-bit words organized into 128 tracks, each with 8192 words consisting of 64 128-word blocks. A word is transferred in 6.4 microseconds, and the drum revolution time is 52 milliseconds.

#### DISPLAY CONTROL AND MONITOR TYPE 346

Plots points, lines, vectors, and characters on a 9%-inch-square raster of 1024 points along each axis. Time between points plotted is 1.5 microseconds in the vector, increment, and character modes. In random point plotting, a time of about 35 microseconds is required per point.

#### DISPLAY MONITOR TYPE 343

Provides additional cathode ray tube display for multiple consoles.

#### HIGH SPEED LIGHT PEN TYPE 370

Detects data displayed by the Types 346 and 343 and inputs identifying signal to the computer.

AUTOMATIC LINE PRINTER AND CONTROL TYPE 646C

Prints 1000 lines a minute, 120 columns a line, any one of 64 characters a column.

AUTOMATIC LINE PRINTER AND CONTROL TYPE 646A

Prints 300 lines a minute, 120 columns a line, any one of 64 characters a column.

#### ANALOG-TO-DIGITAL CONVERTER TYPE 138

Transforms an analog voltage to a binary number, selectable from 6 to 11 bits. Conversion time varies, depending on the number of bits and the accuracy required. Twenty-one combinations of switching point accuracy and number of bits can be selected on the front panel.

MULTIPLEXED ANALOG-TO-DIGITAL CONVERTER TYPE 138/139 The Type 139 Multiplexer Control permits up to 64 channels of analog information to be applied singly to the input of the Type 138 Analog-to-Digital Converter. Channels can be selected in sequence or by individual addresses.

HIGH-SPEED ANALOG-TO-DIGITAL CONVERTER TYPE 142 Transforms an analog voltage to a signed, 10-bit binary number in 6 microseconds. Conversion accuracy is  $\pm 0.15\% \pm 1/2$  least significant bit.

ANALOG-DIGITAL-ANALOG CONVERTER SYSTEM TYPE ADA-1 Performs fast, real-time, data conversion between digital and analog computers. Maximum sample rate for D/A conversion is 200 kc; for A/D and interlaced conversions, 100 kc. Digital word length is 10 bits. Actual conversion times are 5 microseconds for A/D and 2 microseconds for D/A. Semiautomatic features enable the converter system to perform many of the functions that a computer normally

performs for other converter interfaces.

# CHAPTER 2 ARITHMETIC PROCESSOR TYPE 166

The Type 166 is a general purpose processor which performs all of the arithmetic and logical operations in a PDP-6 system and transfers data to and from input-output devices. It is connected to the memory and input-output subsystems through busses and bus interfaces.

The logic block diagram, Figure 4, shows the interconnection of the principal registers of the Type 166, and their functions are described below. An unusual feature of the 166 is that when appropriate the contents of the AR and/or the MQ are transmitted to memory at the end of each instruction. Thus the state of the machine, except for the PC, the four flags, the memory protection and relocation registers, and the executive mode status, is constantly in memory, and there are no instructions that directly reference processor registers except the PC and the flags. Using the AR for the effective address calculation will never destroy a partial result in a calculation. Further, the processor is free to carry out any operation, for example, an I/O operation called for by an interrupt.

#### PROCESSOR REGISTERS

| MA | (Memory Address) An 18-bit register that specifies cation to the memory system.                                                                                                                                            | the desired lo-                      |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| MB | (Memory Buffer) A 36-bit data buffer that commu memory system. The MB is also used as the adderithmetic operations and contains one of the operations.                                                                     | dend register in                     |

| AR | (Arithmetic Register) A 36-bit register used in indexe lations, as an operand register for logical instruct arithmetic and shifting instructions. The accumula the instruction is moved to the AR during most instruction. | tions, and in all tor specified by   |

| MQ | (Multiplier Quotient) A 36-bit register used as an extension operations requiring 72 bits.                                                                                                                                 | ension of the AR                     |

| MI | (Memory Indicator) A 36-bit register used to display memory registers. The MI register is set equal to the memory location specified by the ADDRESS switche processor references the location.                             | contents of the                      |

| PC | (Program Counter) An 18-bit register that contains the tion from which the next instruction is to be taken.                                                                                                                | ne memory loca-                      |

| IR | (Instruction Register) An 18-bit register that contains<br>code, accumulator number, indirect bit, and index<br>for the instruction being executed.                                                                        | s the instruction<br>register number |

| SC | (Shift Counter) A 9-bit register that contains the n a particular part of an instruction is to be repeated. the shifting, floating point, multiply, divide, and by instructions.                                           | This applies to                      |

| FE | (Floating Exponent) A 9-bit register used to store te during floating calculations.                                                                                                                                        | mporary results                      |

MP

(Memory Protection) An 8-bit register used by the executive system in the user mode. This register contains the largest address that can occur in a user's program, that is, the size of the block of memory allocated to the user. When making a reference to memory, the MP and MA registers are compared. If the MA is larger than the MP, the memory cycle does not take place, the memory protection flag is set, and control goes to an executive program with the computer in the executive mode.

RL

(Relocation Register) An 8-bit register used by the executive system in the user mode. If the address in the MA does not exceed the largest address specified by the MP, and is greater than  $17_8$ , the contents of the RL register are added to the high order 8-bits of the MA before the memory cycle takes place.

Figure 4 Data Flow Diagram

In addition to the registers shown in Figure 4, there are several flags important to programming.

AR CRYO Arithmetic register Carry 0. This flag is set when there is a carry from bit 0 of the arithmetic register. AR CRY1 Arithmetic register Carry 1. This flag is set when there is a carry from bit 1 of the arithmetic register. AR OV Arithmetic register Overflow flag. This flag is set when the sign of a result is not consistent with the signs of the operands. PC CHANGE Program Counter Change. This flag is set whenever control is transferred by a skip or jump instruction, except for a JFCL instruction with bit 12 set to 1. PDL OV Push Down List Overflow. A designated accumulator is incremented or decremented by 10000018 during the execution of the push down instructions. This flag is set if a carry from bit 0 occurs. Byte Increment Suppression. This flag, when set to 1, suppresses incrementing during a byte instruction that calls for incrementing. This flag is necessary since a byte instruction may be interrupted between incrementing and the byte operation. In such a case, the incrementing must be suppressed during the first execution of the instruction following the interrupt. The flag is automatically set if such an interrupt occurs. It is cleared before the byte instruction is completed. COUNT CLOCK This flag is set by a CONO instruction. If set, it enables the Clock **ENABLE** flag to cause an interrupt, (See Processor I/O instructions.) CLOCK FLAG This flag is set periodically by a clock. If the Enable flag is set, and if a priority channel is assigned to the processor flags, it causes an interrupt. PC CHANGE This flag is set by a CONO instruction. If set, and a priority channel

ENABLE

has been assigned to the processor flags, it enables the PC Change flag to cause an interrupt.

OV FLAG **ENABLE**

This flag is set by a CONO instruction. If set, and if a priority channel has been assigned to the processor flags, it enables the AR OV flag to cause an interrupt.

EXEC MODE

This mode flip-flop is set when the executive program is running. In the executive mode, the program has access to all of memory. In the user mode (executive mode flip-flop is reset) the protection and relocation registers specify the area of core in which programs may be run. In the user mode illegal memory references and instructions which use the I/O equipment or attempt to halt the computer set the executive mode flip-flop.

Figure 5 The Control Panel

| _              | CONSC         | SOLE CONTROLS AND INDICATORS                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|----------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Lev            | ver Switches  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| ST             | ART 178       | Depressing this switch resets the program counter to the address contained in the ADDRESS switches and starts the processor.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| ilour con car? | Why shaden    | Raising the switch does the same as the above except the machine is started in shadow mode. In the shadow mode, all references to memory locations 0–17 $_8$ go to the core memory rather than to fast memory. The shadow mode is terminated whenever an instruction located above $17_8$ is executed. Therefore, if the address in the ADDRESS switches is greater than $17_8$ , the effect of the switch is the same whether it is raised or depressed. |  |  |  |  |

|                |               | The switch has no effect if the machine is running.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| st.            | OP            | Stops the processor at the end of the memory or instruction cycle. When the switch is in MEMORY STOP position, the read-pause-write mode of operation is inhibited; the machine stops at the end of both the read cycle and write cycle.                                                                                                                                                                                                                  |  |  |  |  |

| CO             | NTINUF        | If the processor has stopped at the end of an instruction or<br>memory cycle, the program may be resumed by depressing<br>this key. The combined use of the STOP and CONTINUE keys<br>has the effect of a single step key.                                                                                                                                                                                                                                |  |  |  |  |

| I/C            | RESET         | Clears the I/O System. & Set exec mode.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| DE             | POSIT         | In the THIS position, the contents of the 36 DATA switches are deposited in the contents of the memory location specified by the ADDRESS switches. The machine will not be stopped if it is running.                                                                                                                                                                                                                                                      |  |  |  |  |

|                |               | In the NEXT position, the memory address register is incremented by one, and the contents of the 36 DATA switches are deposited in the memory location specified by the contents of the memory address register. This key position has no effect if the machine is running.                                                                                                                                                                               |  |  |  |  |

| EX             | AMINE         | In the THIS position, the contents of the memory register addressed by the ADDRESS switches are displayed in the memory indicator lights. If the machine is running, it is not stopped.                                                                                                                                                                                                                                                                   |  |  |  |  |

|                |               | In the NEXT position, the memory address register is incremented by one, and the contents of the memory location specified by the memory address register are displayed in the memory indicator lights. This key position has no effect if the machine is running.                                                                                                                                                                                        |  |  |  |  |

| RE             | ADER ON-OFF   | Turns the power to the perforated tape reader on or off.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| TA             | PE FEED       | Feeds blank tape through the tape punch.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Tog            | ggle Switches | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| co             | NSOLE DISABLE | This is a key-locked switch that disables all control switches that can interfere with the operation of the machine.                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| ADDRESS STOP                                                                                  | Stops the processor each time the contents of the memory address register are equal to the contents of the ADDRESS switches. An adjacent indicator light is on when the switch is on. The existence of an address stop condition inhibits the read-pause-write mode of memory operation, and the machine stops at the end of both the read cycle and write cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REPEAT                                                                                        | If on while a lever switch is held down, the effect is as if the lever switch were being pressed repeatedly with a frequency determined by the setting of the speed knob and vernier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SPEED                                                                                         | Two controls that vary the repeat interval when the REPEAT switch is on. The left knob is a six-position coarse control giving speed ranges from 3.4 microseconds and increasing by a factor of ten up to 340 milliseconds. The right knob is a continuously variable fine control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| POWER                                                                                         | Turns on power to the processor and all equipment connected to it.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MEMORY DISABLE                                                                                | This switch inhibits the non-existent memory continue pulse. If a non-existent area of memory is addressed, the non-existent memory flag is set; and if the MEMORY DISABLE switch is on, the machine stops.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DATA                                                                                          | Up to 36 bits of information can be inserted for transfer to memory when the DEPOSIT switch is pressed. (May be examined under program control. See I/O Programming for Type 166 Processor.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                               | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ADDRESS                                                                                       | There are 18 address switches which are used with various keys and switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ADDRESS Indicator Lights                                                                      | There are 18 address switches which are used with various                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                               | There are 18 address switches which are used with various keys and switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Indicator Lights                                                                              | There are 18 address switches which are used with various keys and switches.  Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Indicator Lights  INSTRUCTION                                                                 | There are 18 address switches which are used with various keys and switches.  Function  Displays bits 0–8 of the instruction register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Indicator Lights  INSTRUCTION                                                                 | There are 18 address switches which are used with various keys and switches.  Function  Displays bits 0–8 of the instruction register.  Displays bits 9–12 of the instruction register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Indicator Lights  INSTRUCTION  AC                                                             | There are 18 address switches which are used with various keys and switches.  Function  Displays bits 0–8 of the instruction register.  Displays bits 9–12 of the instruction register.  Displays bit 13 of the instruction register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Indicator Lights  INSTRUCTION  AC  I INDEX                                                    | There are 18 address switches which are used with various keys and switches.  Function  Displays bits 0–8 of the instruction register.  Displays bits 9–12 of the instruction register.  Displays bit 13 of the instruction register.  Displays bits 14–17 of the instruction register.  Displays the contents of the memory register addressed by the ADDRESS switches. The MI is set whenever the EXAMINE                                                                                                                                                                                                                                                                                                                                                                                         |

| Indicator Lights  INSTRUCTION  AC  I INDEX  MEMORY INDICATION                                 | There are 18 address switches which are used with various keys and switches.  Function  Displays bits 0–8 of the instruction register.  Displays bits 9–12 of the instruction register.  Displays bit 13 of the instruction register.  Displays bits 14–17 of the instruction register.  Displays the contents of the memory register addressed by the ADDRESS switches. The MI is set whenever the EXAMINE key is operated or the program references the register.  Displays the contents of the program counter. When the processor stops, the program counter will be pointing to the                                                                                                                                                                                                            |

| Indicator Lights  INSTRUCTION  AC I INDEX  MEMORY INDICATION  PROGRAM COUNTER                 | There are 18 address switches which are used with various keys and switches.  Function  Displays bits 0–8 of the instruction register.  Displays bits 9–12 of the instruction register.  Displays bit 13 of the instruction register.  Displays bits 14–17 of the instruction register.  Displays the contents of the memory register addressed by the ADDRESS switches. The MI is set whenever the EXAMINE key is operated or the program references the register.  Displays the contents of the program counter. When the processor stops, the program counter will be pointing to the next instruction.  Display the last location referenced in memory before the machine stopped. If the machine stopped on a halt instruction (JRST 4),                                                       |

| Indicator Lights  INSTRUCTION  AC I INDEX  MEMORY INDICATION  PROGRAM COUNTER  MEMORY ADDRESS | There are 18 address switches which are used with various keys and switches.  Function  Displays bits 0–8 of the instruction register.  Displays bits 9–12 of the instruction register.  Displays bits 13 of the instruction register.  Displays bits 14–17 of the instruction register.  Displays the contents of the memory register addressed by the ADDRESS switches. The MI is set whenever the EXAMINE key is operated or the program references the register.  Displays the contents of the program counter. When the processor stops, the program counter will be pointing to the next instruction.  Display the last location referenced in memory before the machine stopped. If the machine stopped on a halt instruction (JRST 4), the MA contains the address of the halt instruction. |

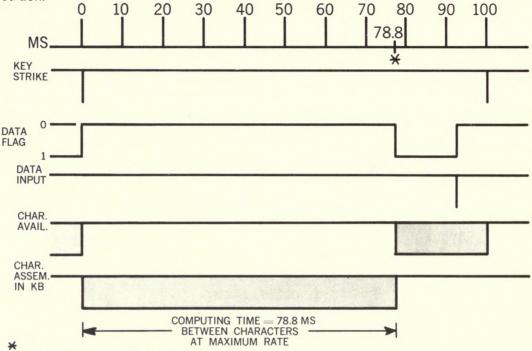

| Indicator Lights | Function                                                |